# A 32GHz Transformer Based Differential SPST CMOS switch

Seungchan Lee<sup>1</sup> and Songcheol Hong<sup>a</sup>

School of Electrical Engineering, KAIST E-mail : eyeswinter@kaist.ac.kr

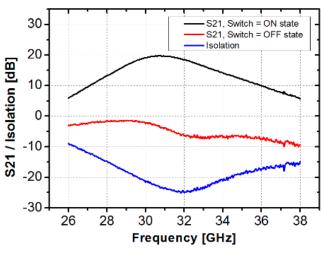

*Abstract* - A 32GHz transformer based single-pole single-throw (SPST) switch is presented, that is integrated with a low noise amplifier (LNA) in a 65-nm bulk CMOS process. The proposed switch has a series resonance structure at shunt path between differential signal lines to increase isolation when the switch is in off state. It reduces the insertion loss of an entire system by embedding the post matching circuit (LNA input matching network) when the switch is in on state. The measured insertion loss difference between LNA and proposed SPST switch integrated LNA chip is less than 1.35 dB at 30-36 GHz, and the isolation is 25 dB at 32 GHz. The core area of SPST switch is 350 um x 220 um.

### I. INTRODUCTION

Upcoming various millimeter-wave (mm-wave) systems need small size and low loss switches to have reconfigurable circuits. For example, beamforming front-end ICs in mm-wave 5G mobile communication system have to use the switches for antenna to select transmit and receive paths. They have to be carefully designed to have low insertion losses at on state and high isolations at off state, which influence seriously on communication qualities.

The performances of switches at mm-wave frequency are degraded due to the effects of parasitic ground path's inductances. The switch performance is also determined by the product of Ron resistance and Coff capacitance. By reducing the Ron in the case of the series switch, one can reduce the insertion loss, and one can improve the isolation by reducing the Coff. However, the switch performance degrades as frequency increases because Coff capacitance's impedance is in inverse proportion to the frequency, which degrades is

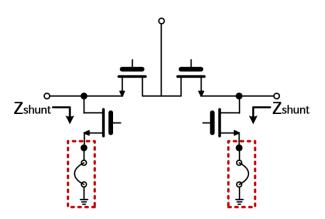

olations. Also, as explained in Fig. 1, shunt switch's performance is largely limited by the parasitic ground path's inductance at the mm-wave frequency because the impedance of the ground inductor (Zshunt in Fig. 1) is proportional to the frequency.

a. Corresponding author; songcheol1234@gmail.com

Copyright ©2017 IDEC All rights reserved.

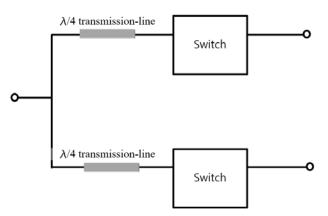

Therefore, the series-shunt structure is commonly used only at a few GHz frequency [1]. To overcome these performance limitations of transistor based switches at high frequencies, the switches with quarter-wave transmission lines are conventionally used as shown in Fig. 2 [2]. However, the transmission line based structure is too large at the mm-wave 5G communication frequencies of ~30GHz to be used in integrated circuits. Therefore, there must be strong demands for small size and low loss switches.

In this paper, we propose a transformer-based SPST switch that includes the input matching network of a following LNA. By including the matching network of the LNA, one can implement the size-efficient and low loss SPST switch.

Fig. 1. Transistor based switch structure (series-shunt)

Fig. 2. Quarter-wave transmission line based switch structure.

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

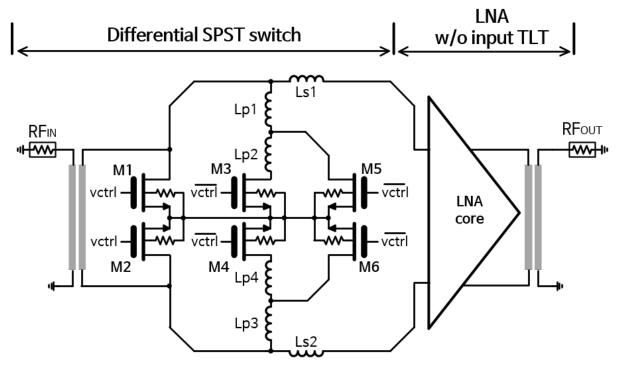

Fig. 3. Schematics of the proposed SPST switch

| TABLE I.                                                         |

|------------------------------------------------------------------|

| Transistor parameters and inductance of the proposed SPST switch |

| Transistor name | Transistor size<br>W/L[um/um] | Inductor name | Inductance[pH] |

|-----------------|-------------------------------|---------------|----------------|

| M1, M2, M3, M4  | 96/0.06                       | Lp1, Lp3      | 100            |

| M5, M6          | 192/0.06                      | Lp2, Lp4      | 90             |

|                 |                               | Ls1, Ls2      | 160            |

#### II. CIRCUIT DESIGN

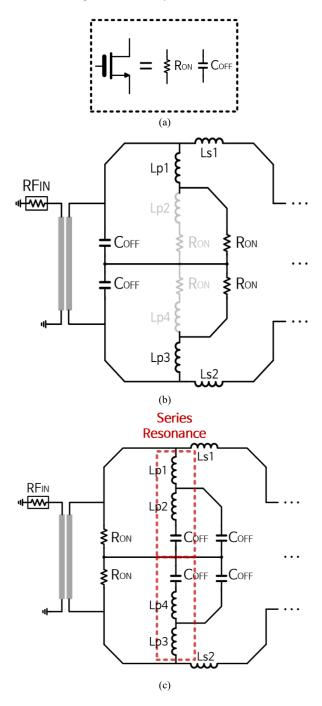

Fig. 3 shows the schematic of the proposed SPST switch that has a transformer based differential structure with a following LNA. The proposed SPST switch consists of a single to differential transmission-line transformer and shunt switch network. The transistor parameters of the switch and inductor size are listed in Table I. Also, Fig. 4 shows equivalent circuits represented by a simplified model of transistors with  $R_{on}$  and  $C_{off}$ .

## A. Pass mode

When the switch is in on state, M1 & M2 is off and M3 – M6 is on in Fig. 4 (b). In this condition, one can ignore  $L_{p2}$ , M3,  $L_{p4}$ , and M4 because of low  $R_{on}$  impedance of large size transistor M5 and M6. Finally, 1:1 transformer,  $L_{s1}$  &  $L_{s2}$ ,  $L_{p1}$  &  $L_{p3}$ , and off capacitances of M1 & M2 form the input matching network of the following LNA to make low loss and small size switch.

As mentioned above, the switch operates as an input

matching network of the following LNA. There are no additional matching network between the switch and the LNA that results in the reduction of the insertion loss and the chip size compared to conventional SPST switches.

#### B. Isolation mode

Also, as shown in Fig. 4 (c), by using differential structure, one can ignore the effects of ground path's parasitic inductances that degrades the isolation of shunt switch. To make use of the virtual ground, perfect differential signals must be introduced. A large decoupling capacitor at the center tap of the secondary transformer is introduced to make good virtual ground. This allows to make good differential signals and results in better isolation.

To improve the isolation of the switch further, the series resonance at shunt path between the differential signal paths is introduced at the frequency when the switch is in off state. Finally, due to the shunt transistors (M1 and M2) and series resonance path (Lp1, Lp2, M3 and Lp3, Lp4, M4), the proposed switch can have good isolation.

Fig. 4. Equivalent circuits of the proposed SPST switch (a) Simplified transistor model (b) Pass mode (c) Isolation mode

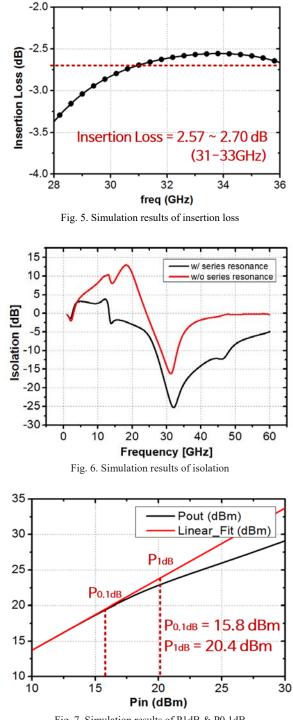

As in Fig. 5, the simulation results of the insertion loss that includes input matching network of the following LNA is about  $2.53 \sim 2.70$  dB that corresponds to only about 1.2 dB loss without the loss of the input matching network. This is considerably low compared to those of separate switches.

Also, as in Fig. 6, the isolation is about 25.9 dB when the switch is in off state. Due to the series resonance of the shunt path, additional 10 dB isolation at 32GHz is achieved. Also, the  $P_{1dB}$  is 20.4dBm and  $P_{0.1dB}$  (=0.1dB compression point) is 15.8dBm as in Fig. 7. This high  $P_{0.1dB}$  is enough to meet linearity of various systems. By using the embedded concept and series resonance, the proposed switch has low loss, size efficient, high isolation, and high linearity.

Fig. 7. Simulation results of P1dB & P0.1dB

III. IMPLEMENTATION AND MEASUREMENT

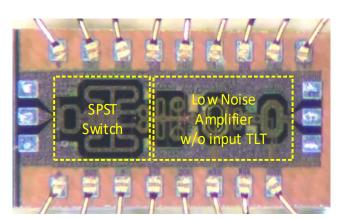

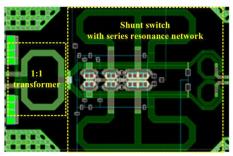

The proposed SPST switch was implemented in a 1P9M 65nm CMOS process. Fig. 8 shows a microphotograph of the proposed switch. The area of the switch core is 350 um x 220 um (0.077mm<sup>2</sup>). S-parameter measurements are done using a 67-GHz Anritsu 37397D VNA.

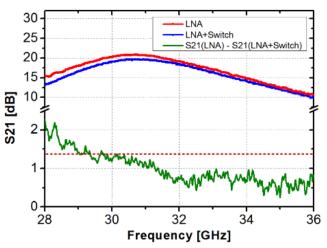

Fig. 10 shows the insertion loss of the switch by subtracting the gain of LNA and switch integrated LNA. The SPST switch integrated LNA shows only additional 1.35 dB loss compared to the gain of LNA. This is because of the

| TABLE II.                                              |  |  |  |  |  |

|--------------------------------------------------------|--|--|--|--|--|

| Comparison table with the prior works of SPST switches |  |  |  |  |  |

| Parameters          | This work                                         | [3]      | [4]           | [5]   |

|---------------------|---------------------------------------------------|----------|---------------|-------|

| Technology(nm)      | 65nm                                              | 65nm     | 130nm         | 65nm  |

| Frequency (GHz)     | 30-36                                             | 57-66    | 35            | 54-84 |

| Insertion loss (dB) | < 1.35<br>(Difference between LNA and SPST + LNA) | 1.6 -2.2 | 1.0, 1.8, 2.6 | 1.7   |

| Isolation (dB)      | 25 @ 32GHz                                        | 27       | 10, 32, 26    | 35    |

| P1dB (dBm)          | *20.4                                             | 11       | 15, >22, 12   | 10.5  |

# \* Simulation

matching circuit embedded structure of the switch. Fig. 11 shows the measured results of switch isolation that is more than 25 dB at 32 GHz. The isolation is improved by introducing the series resonance to the shunt path at the center frequency of 32GHz that is well agreed with the simulated result.

Fig. 8. Chip microphotograph

Fig. 9. Switch core layout

Fig. 10. Measured results of insertion loss difference between LNA and SPST integrated LNA

Fig. 11. Measured results of switch isolation

IDEC Journal of Integrated Circuits and Systems, VOL 3, No.4, Oct. 2017

#### IV. CONCLUSIONS

A transformer-based differential SPST switch that is integrated to the LNA is presented. The switch includes the LNA input matching network and resonance network that improves the insertion loss and isolation. The switch shows the additional insertion loss of less than 1.35 dB by comparing the LNA with an input matching network at 30 to 36 GHz and the isolation of 25 dB at 32 GHz.

## ACKNOWLEDGMENT

This work was supported by the Korea Government (MEST) under National Research Foundation of Korea (NRF) Grant 2017R1A2A1A05001361. The authors would like to thank the Integrated Circuit Design Education Center (IDEC) for their support with computer-aided design (CAD) tools.

#### REFERENCES

- [1] Mei-Chao Yeh, Zuo-Min Tsai, Ren-Chieh Liu, K. Y. Lin, Ying-Tang Chang and Huei Wang, "Design and analysis for a miniature CMOS SPDT switch using body-floating technique to improve power performance," in IEEE Transactions on Microwave Theory and Techniques, vol. 54, no. 1, pp. 31-39, Jan. 2006.

- [2] C. W. Byeon and C. S. Park, "Design and Analysis of the Millimeter-Wave SPDT Switch for TDD Applications," in IEEE Transactions on Microwave Theory and Techniques, vol. 61, no. 8, pp. 2858-2864, Aug. 2013.

- [3] J. He and Y. P. Zhang, "Design of SPST/SPDT Switches in 65nm CMOS for 60GHz applications," 2008 Asia-Pacific Microwave Conference, Macau, 2008, pp. 1-4.

- [4] B. W. Min and G. M. Rebeiz, "Ka-Band Low-Loss and High-Isolation Switch Design in 0.13-um CMOS," in IEEE Transactions on Microwave Theory and Techniques, vol. 56, no. 6, pp. 1364-1371, June 2008.

- [5] R. Shu, J. Li, A. Tang, B. J. Drouin and Q. J. Gu, "Coupling-Inductor-Based Hybrid mm-Wave CMOS SPST Switch," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 64, no. 4, pp. 367-371, April 2017.

- [6] Zhenbiao Li and K. K. O, "15-GHz fully integrated nMOS switches in a 0.13-µm CMOS process," in IEEE Journal of Solid-State Circuits, vol. 40, no. 11, pp. 2323-2328, Nov. 2005.

- [7] Q. Li and Y. P. Zhang, "CMOS T/R Switch Design: Towards Ultra-Wideband and Higher Frequency," in IEEE Journal of Solid-State Circuits, vol. 42, no. 3, pp. 563-570, March 2007.

- [8] Y. P. Zhang, Q. Li, W. Fan, C. H. Ang and H. Li, "A Differential CMOS T/R Switch for Multistandard Applications," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 53, no. 8, pp. 782-786, Aug. 2006.

- [9] J. He, Y. Z. Xiong and Y. P. Zhang, "Analysis and Design of 60-GHz SPDT Switch in 130-nm CMOS," in IEEE Transactions on Microwave Theory and Techniques, vol. 60, no. 10, pp. 3113-3119, Oct. 2012.

- [10] S. F. Chao, H. Wang, C. Y. Su and J. G. J. Chern, "A 50 to 94-GHz CMOS SPDT Switch Using Traveling-Wave Concept," in IEEE Microwave and Wireless Components Letters, vol. 17, no. 2, pp. 130-132, Feb. 2007.

- [11] Q. Li, Y. P. Zhang, K. S. Yeo and W. M. Lim, "16.6and 28-GHz Fully Integrated CMOS RF Switches With Improved Body Floating," in IEEE Transactions on Microwave Theory and Techniques, vol. 56, no. 2, pp. 339-345, Feb. 2008.

- [12] P. Park, Dong Hun Shin, J. J. Pekarik, M. Rodwell and C. P. Yue, "A high-linearity, LC-Tuned, 24-GHz T/R switch in 90-nm CMOS," 2008 IEEE Radio Frequency Integrated Circuits Symposium, Atlanta, GA, 2008, pp. 369-372.

- [13] Zhenbiao Li, Hyun Yoon, Feng-Jung Huang and K. K. O, "5.8-GHz CMOS T/R switches with high and low substrate resistances in a 0.18-µm CMOS process," in IEEE Microwave and Wireless Components Letters, vol. 13, no. 1, pp. 1-3, Jan. 2003.

- [14] X. J. Li and Y. P. Zhang, "Flipping the CMOS Switch," in IEEE Microwave Magazine, vol. 11, no. 1, pp. 86-96, Feb. 2010.

- [15] M. Uzunkol and G. Rebeiz, "A Low-Loss 50-70 GHz

- SPDT Switch in 90 nm CMOS," in IEEE Journal of Solid-State Circuits, vol. 45, no. 10, pp. 2003-2007, Oct. 2010.

- [16] M. Hangai, K. Nakahara, M. Yamaguchi and M. Hieda, "A Ka-band high-power protection switch with open/short-stub selectable circuits," 2009 IEEE MTT-S International Microwave Symposium Digest, Boston, MA, 2009, pp. 1513-1516.

- [17] S. L. Liu, M. H. Wu and A. Chin, "Design of a CMOS T/R Switch With High Power Capability: Using Asymmetric Transistors," in IEEE Microwave and Wireless Components Letters, vol. 22, no. 12, pp. 645-647, Dec. 2012.

Seungchan Lee received the B.S. and M.S. degrees in electrical engineering from Korea Advanced Institute of Science and Technology KAIST), Daejeon, Korea, in 2015 and 2017. And he is currently working toward the Ph.D. degree in electrical engineering at KAIST.

His research interests are RF IC

design for wireless communication.

**Songcheol Hong** (S'87–M'88) received the B.S. and M.S. degrees in electronics from Seoul National University, Seoul, Korea, in 1982 and 1984, respectively, and the Ph.D. degree in electrical engineering from the University of Michigan at Ann Arbor in 1989. Since May 1989, he has been with the faculty of the Department of Electrical

Engineering and Computer Science, Korea Advanced Institute of Science and Technology, Daejeon, Korea. In 1997, he held short visiting professorships with Stanford University, Palo Alto, CA, and Samsung Microwave Semiconductor, Suwon, Korea. His research interests are microwave integrated circuits and systems, including power amplifiers for mobile communications, miniaturized radar, millimeter-wave frequency synthesizers, and novel semiconductor devices.