# CMOS 65nm Active 2-port Inductor using tunable feedback resistance

# Jageon Koo and Yongchae Jeong

Division of electronics and information Engineering, Chonbuk National University E-mail: zxsq123@jbnu.ac.kr

Abstract - In this paper, a novel CMOS high Q-factor active 2-port inductor with feedback resistor has been proposed, mathematically analyzed and fabricated. The proposed circuit topology can improve its equivalent inductance range and Q-factor. The proposed active 2-port inductor was implemented by 65 nm Samsung RF CMOS technology, which demonstrates a maximum quality-factor of 600 with 3 nH inductance. The fabricated circuit occupies 200 um x 300 um chip size and has high Q-factor and inductance over wide operating frequency range as compared to the conventional active 2-port inductor circuits. In addition, the inductance variation is very small in wide operating frequency range.

#### I. INTRODUCTION

With increasing demands of wireless communication system, a low cost and high integration process technologies are required to reduce the production cost and the system dimension. For these requirements, the CMOS technology has become one of the best choices for RF circuits and systems. In CMOS technology, a spiral inductor is widely used, however, it occupies large circuit size and has low Q-factor which can decrease performances of RF circuits and systems due to high insertion loss [1]. The active inductor has become the attractive alternative solution of spiral, which can provide high Q-factor and inductances. Therefore, in recent years, researches on 1-port active inductor are widely conducted and can be realized with gyrator-C structure [2], [3]. Since 1-port active inductor is grounded type 1-port network, it cannot be used as two-port network.

To solve this problem, 2-port active inductor was implemented in previous research works [4], [5], [6]. However, the conventional 2-port active inductor requires the differential input modes and have several disadvantages such as narrow bandwidth for high-Q factor and large inductance variation [7].

In this paper, we proposed novel 2-port active inductor with feedback resistance. We analyzed a conventional circuit

by applying RF small signal model of a transistor. Using this analysis result, we proposed the optimum design method of proposed circuit for wideband operation range with high Q-factor and small variance inductance by adding feedback resistance.

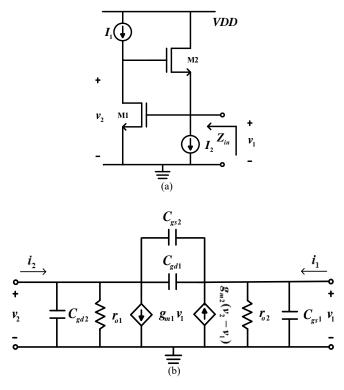

Fig. 1. (a) Schematic of grounded active inductor and (b) its small signal equivalent circuit.

### II. THEORY OF ACTIVE INDUCTOR

# A. 2-port Active inductor with LC resonator

The gyrator structure is typically used in the grounded active inductor which consists of two transistors and generates an inductive reactance from parasitic capacitances of those transistors. Fig. 1 shows a structure of grounded active inductor and its small signal equivalent circuit. From the small signal equivalent circuit, we can derive the 2-port admittance matrix. The input impedance of grounded active-inductor shown in Fig.1 is represented as (1).

This is an Open-Access article distributed under the terms of the Creative Commons Attribution Non-Commercial License (http://creativecommons.org/licenses/by-nc/3.0) which permits unrestricted non-commercial use, distribution, and reproduction in any medium, provided the original work is properly cited.

a. Corresponding author; ycjeong@jbnu.ac.kr

Copyright ©2016 IDEC All rights reserved.

$$Z_{in} = \frac{\frac{1}{r_{o1}} + s\left(C_{gs2} + C_{gd1} + C_{gd2}\right)}{\left[g_{m2} + \frac{1}{r_{o2}} + s\left(C_{gs1} + C_{gs2} + C_{gd1}\right)\right]\left[\frac{1}{r_{o1}} + s\left(C_{gs2} + C_{gd1} + C_{gd2}\right)\right]} + \left[g_{m2} + s\left(C_{gs1} + C_{gd1}\right)\right]\left[g_{m1} - s\left(C_{gs2} + C_{gd1}\right)\right]}$$

(1)

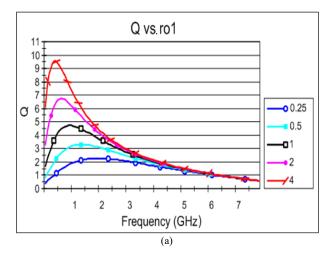

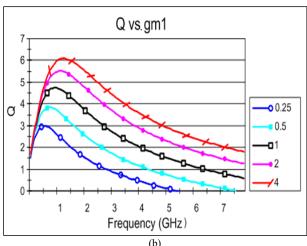

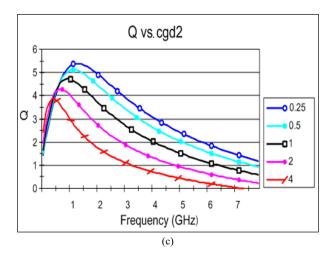

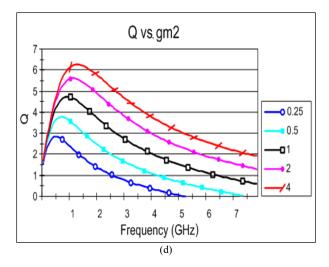

Fig. 2. The simulated Q-factor of the conventional grounded active inductor for (a)  $r_{o1}$  variation, (b)  $g_{m1}$  variation, (c)  $C_{gs1}$  variation and (d)  $C_{gs2}$  variation.

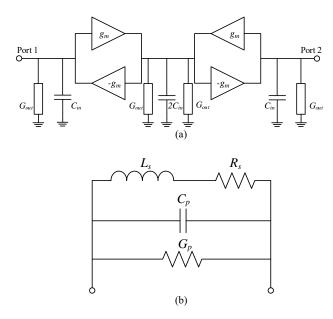

Fig. 3. (a) Gyrator-based 2-port active inductor and (b) its equivalent circuit.

Using the approximate relationship,  $sC_{parasitic} > g_m \gg 1/r_o$ , the input impedance of the grounded active inductor presented in (1) can be simplified as (2). Using (2), we can know this structure can be operated as the inductance.

$$Z_{in} = \frac{s\left(C_{gs2} + C_{gd1} + C_{gd2}\right)}{g_{m1}g_{m2}} = sL$$

(2)

However, we cannot say that those parameters have an effect on Q-factor from Eq. (2). So, we can observe the variation of Q-factor through frequency by varying typical parameters in Eq. (3) from mathematical simulation.

$$Q = \frac{\omega L}{R} = \frac{\omega \left[ (C_T + C_{ds2}) (C - \omega^2 A) - (B/r_{o1}) \right]}{\omega^2 B (C_T + C_{ds2}) + (C - \omega^2 A)/r_{o1}}$$

(3)

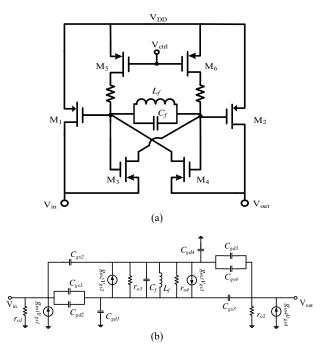

Fig. 4. Proposed two ports active inductor using LC resonators: (a) schematic and (b) small signal model.

The simulation results are shown in Fig. 2. Fig. 2(a) shows that Q-factor can be enhanced by increasing  $r_{o1}$  of transistor M1. Fig. 2(b) shows that Q-factor is proportional to  $g_{m1}$ , although the inductance value is inverse proportional to  $g_{m1}$  as it is represented in Eq. (2). Fig. 2(c) and Fig. 2(d) shows that Q-factor can be decreased by increasing  $C_{gs2}$ . We can find that Q-factor is changed dynamically by the effect of parasitic capacitance of  $M_2$  at high frequency.

However, the conventional grounded active inductor topologies cannot be used with other circuits in series. Therefore, in this work, we propose the 2-port active inductor which can be used in series with other circuits.

The conventional 2-port active inductor can be designed by cascading two gyrators as shown in Fig. 3(a). The parasitic components of the transconductance can be expressed as  $G_{out}$  and  $C_{in}$ . From this circuit, we can obtain Y-parameters as (4).

$$Y_{11} = Y_{22} = \left(G_{out} + j\omega C_{in} + \frac{g_m^2}{2G_{out} + 2j\omega C_{in}}\right)$$

(4a)

$$Y_{21} = Y_{12} = \frac{-g_m^2}{2G_{out} + 2j\omega C_{in}}$$

(4b)

The equivalent circuit of the 2-port active inductor is shown in Fig. 3(b). In this structure, we assume that the two gyrators have same input and output parasitic components. The circuit element values of the equivalent model can be found as (5).

$$R_{s} = 2G_{out}/g_{m}^{2} \tag{5a}$$

$$L_{\rm s} = 2C_{\rm in}/g_{\rm m}^2 \tag{5b}$$

$$C_{p} = C_{in} \tag{5c}$$

$$G_p = G_{out} (5d)$$

Fig. 5. Proposed two port active inductor using feedback resistor: (a) schematic and (b) small signal model.

The Q-factor is mainly determined by the series resistance  $R_s$  and shunt conductance  $G_p$ . These values are related to the output admittance  $G_{out}$  as shown in (5a) and (5d). This conventional 2-port active inductor has several drawbacks such as low Q-factor, high power consumption, and narrow operating range. In this paper, we proposed the novel high Q-factor active 2-port inductor by decreasing output admittance with the parallel LC resonator.

# B. 2-port active inductor using feedback resistor

The 2-port active inductor using feedback resistance is shown in Fig. 5. In this structure, transistors  $M_1$  and  $M_2$  are operating with positive transconductance amplifier whereas  $M_3$  and  $M_4$  with negative transconductance amplifier. Transistors  $M_5$ - $M_6$  are connected for bias current sources, and  $M_3$  and  $M_4$  are connected in cross coupled pair. The feedback resistor  $R_f$  has been addend between drain of  $M_3$  and  $M_4$ . Fig. 5(b) shows small-signal model of proposed active 2-port inductor. By deriving the port voltage  $V_{in}$  and input current  $I_{in}$ , the input impedance  $Z_{in}$  can be obtained as (6).

$$Z_{in} = 2 \frac{\left(g_{m1} + g_{m3}\right) \left[g_{ds5} - g_{m1}\left(R_{f}g_{ds5} + 1\right)\right] + \omega^{2}\left(C_{gs1} + C_{gs3}\right)^{2}\left(R_{f}g_{ds5} + 1\right)}{g_{ds5}\left[\left(g_{m1} + g_{m3}\right)^{2} + \omega^{2}\left(C_{gs1} + C_{gs3}\right)^{2}\right]} + j2 \frac{\omega\left(C_{gs1} + C_{gs3}\right) \left[\left(R_{f}g_{ds5} + 1\right)\left(2g_{m1} + g_{m3}\right) - g_{ds5}\right]}{g_{ds5}\left[\left(g_{m1} + g_{m3}\right)^{2} + \omega^{2}\left(C_{gs1} + C_{gs3}\right)^{2}\right]}$$

$$(6)$$

From  $Z_{in}$ , the equivalent R and L can be obtained as (7)

$$R_{eq} = 2 \frac{\left(g_{m1} + g_{m3}\right) \left[g_{ds5} - g_{m1}\left(R_f g_{ds5} + 1\right)\right] + \omega^2 \left(C_{gs1} + C_{gs3}\right)^2 \left(R_f g_{ds5} + 1\right)}{g_{ds5} \left[\left(g_{m1} + g_{m3}\right)^2 + \omega^2 \left(C_{gs1} + C_{gs3}\right)^2\right]}$$

(7a)

$$L_{eq} = 2 \frac{\left(C_{gs1} + C_{gs3}\right) \left[\left(R_f g_{ds5} + 1\right) \left(2g_{m1} + g_{m3}\right) - g_{ds5}\right]}{g_{ds5} \left[\left(g_{m1} + g_{m3}\right)^2 + \omega^2 \left(C_{gs1} + C_{gs3}\right)^2\right]}$$

(7b)

The Q-factor of the active inductor is also calculated from the small signal model analysis and is given as (8)

$$Q = \left(\frac{\omega L}{R_s}\right) \frac{1}{1 + R_s G_p \left[1 + \left(\frac{\omega L}{R_s}\right)^2\right]}$$

(8)

As observed from (7a), the value of the feedback resistor  $R_f$  effects to decrease the equivalent resistance which results in improvement of the Q-factor.

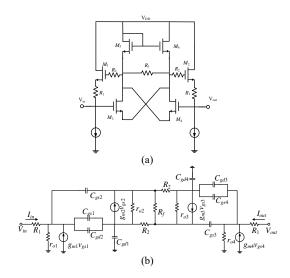

#### III. PROPOSED 2-PORT ACTIVE INDUCTOR

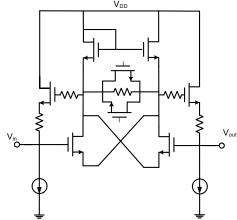

Fig. 6. Proposed 2-port active inductor using tunable resistance.

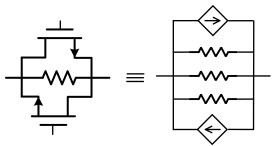

Fig. 7. Equivalent circuit of tunable feedback resistor.

The proposed 2-port active inductor is shown in Fig. 6. In this proposed structure, connected the tunable resistance instead of the feedback resistance. This feedback resistance can variation the inductance of proposed circuit. Also connected opposite pair therefore to get a symmetric characteristic. Fig. 7 shows the equivalent circuit of tunable feedback resistor. When the gate voltage is change, current of current source is changed, therefore equivalent resistance of feedback resistance can be change.

From Fig.3, we can know increase the output resistor that can improve Q-factor. Therefore, the LC resonator is connected between drain of  $M_3$  and  $M_4$ . This resonator can increase output impedance of  $M_3$  and  $M_4$  as well as can reduce parasitic capacitances of  $M_1$  and  $M_2$ , and decrease the equivalent parallel capacitance. When parallel capacitance decreases, the operating frequency range can be increased.

The power consumption is one of the important issues for the active inductor. If the power consumption of active-inductor increase, the overall systems power consumption will be increased. Therefore, in this work we chose small  $g_m$  for small power consumption. However, the small  $g_m$  can increase the equivalent series resistance.

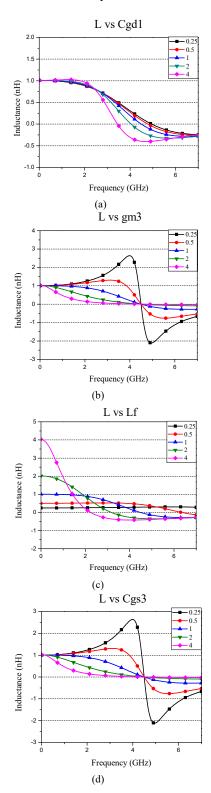

Fig. 8. The simulated inductance of the proposed grounded active inductor for (a)  $C_{gd1}$  variation, (b)  $g_{m3}$  variation, (c)  $C_{gs3}$  variation and (d)  $L_f$  variation.

#### V. EXPERIMENTAL RESULTS

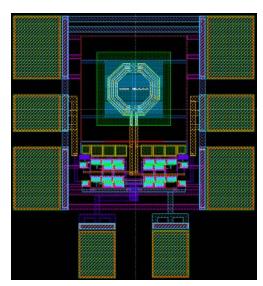

The proposed circuit was fabricated using 65 nm Samsung CMOS process. The simulation was performed in Cadence Spectre by using SP simulation. Fig. 9 shows the layout of the proposed circuit. The overall circuit size of the designed 2-port active inductor including pad is 0.4 mm X 0.45 mm and core is only 0.2 mm X 0.3 mm. The proposed circuit consumes 3.6 mW DC power at 1.2 V supply voltage. On wafer probing was used to characterize 2-port S-parameters of the proposed circuit and also for de-embedding the parasitic components.

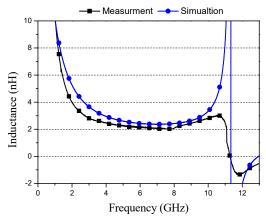

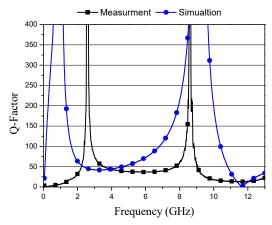

Fig. 10 and 11 show the simulated and measured inductances and Q-factors of the fabricated circuit. From the experiment, it is found that the inductance and Q-factor are higher than 2 nH and 35, respectively, in the frequency range of 3 ~ 10 GHz. The maximum inductance is 22 nH at low frequency and maximum Q-factor is 450 at 2.7 GHz. The performance comparison of the proposed CMOS active inductor with state-of art is summarized in Table I. The operating frequency of proposed circuit is wider than conventional ones [4], [5], [7]. Also the proposed circuit has low power consumption, high Q-factor, and small chip size. Moreover, although inductance is lower than previous works, the proposed circuit provides constant inductance over wider frequency range.

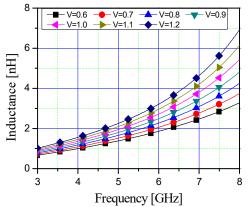

Fig. 12 show the measurement inductances of the proposed tunable active inductor. From the experiment, it is found that the inductance is can be varied 1.5 to 5 nH, in the frequency range of  $3 \sim 8$  GHz. The maximum inductance is 7.5 nH at 8 GHz. Also the proposed circuit consumption 3 mA at the 1.2 V supply DC voltage. The chip occupies 650 x 450 um² including bonding pad and 450 x 480 um without bonding pad. Moreover, although inductance is lower than previous works, the proposed circuit provides constant inductance over wider frequency.

Fig. 9. Layout of proposed active inductor.

TABLE I.

Performance Comparison of CMOS 2-Port active inductor.

| Items\Ref.              | [4]  | [5]  | [7]   | this work |

|-------------------------|------|------|-------|-----------|

| Technology (nm)         | 180  | 180  | 180   | 65        |

| Freq. range (GHz)       | 1-2  | 1-5  | 1-5   | 3-10      |

| L <sub>max.</sub> (nH)  | 27   | 35   | 22.4  | 22        |

| Q-factor                | 28   | 68   | 500   | 450       |

| Size (mm <sup>2</sup> ) | 0.01 | 0.16 | 0.075 | 0.06      |

| P <sub>DC</sub> (mW)    | 4    | 3.6  | 4.5   | 3.6       |

Fig. 10. Simulated and measured inductance of the proposed active inductor

Fig. 11. Simulated and measured Q-factor of the proposed active inductor.

Fig. 12. Measurement results of the proposed circuit.

#### VI. CONCLUSIONS

In this paper we proposed the novel 2-port inductor using feedback LC resonator. The proposed circuits shows inductance of 2 nH and Q-factor higher than 35 at in frequency range of 3~10 GHz. Also, the designed circuit provides high Q-factor and small variance inductance in wide frequency range. The overall circuit size of proposed active inductor is reduced by 25% for the same inductance of spiral inductor. In a future, we will apply the proposed 2-port active inductor in designing RF circuits and systems such as Wilkinson power divider, directional coupler, RFIC filters, and LC-VCO.

#### ACKNOWLEDGMENT

This work was supported by the IDCE (IC Design Education Center).

#### REFERENCES

- [1] A. Zolfaghari, A. Chan, and B. Razavi, "Stacked inductors and transformers in CMOS technology," *IEEE Journal of Solid-State Circuit*, vol. 36, no. 4, pp. 620-628, Apr. 2001.

- [2] A. Thanachayanont, "CMOS transistor only active inductor for IF/RF applications," in *Proceedings of IEEE International Conference on Industrial Technology*, vol. 2, pp. 1209-1212, 2002.

- [3] S. Seo, N. Ryu, H. Choi, and Y. Jeong, "Novel high-Q inductor using active inductor structure and feedback parallel resonance circuit," in *Proceedings of IEEE Radio Frequency Integrated Circuits Symposium*, pp. 467-470, 2007.

- [4] K. Hwang, C. Cho, J. Lee, and J. Kim, "High quality-factor and inductance of symmetric differential-pair structure active inductor using a feedback resistance design," in *IEEE International Microwave Symposium Digest*, pp. 1059-1062, 2008.

- [5] Lai. Q and Mao. J, "A new floating active inductor using resistive feedback technique," in *IEEE International Microwave Symposium Digest*, pp. 1748-1751, 2010.

- [6] G. Zhang and L. Gautier, "Broad-band lossless monolithic microwave active floating inductor," *IEEE Microwave and Guided Wave Letters*, vol. 3, no. 4, pp. 98-100, Apr. 1993.

- [7] H. Feng and K. Mouthaan, "Lossless CMOS active reciprocal two-port inductor and application in a series LC filter," in European Microw. Conf., pp. 364-367, 2012.

Jageon Koo received the B.S. degree in electrical engineering from Chonbuk University, Jeonju, Korea, in 2016 and is currently working toward the M.S. degree in electrical engineering from Chonbuk National University, Jeonju Korea.

His main interests are RF integrated circuits for wireless communications, especially CMOS

passive circuit using active device.

Yongchae Jeong (M'99–SM'10) received the B.S.E.E., M.S.E.E., and Ph.D. degrees in electronics engineering from Sogang University, Seoul, Korea, in 1989, 1991, and 1996, respectively. From 1991 to 1998, he was a Senior Engineer with Samsung Electronics. From 1998, he joined the Division of Electronics Engineering, Chonbuk National University, Jollabuk-do, Korea.

From July 2006 to December 2007, he was with the Georgia Institute of Technology, as a Visiting Professor. He is currently a Professor and member of the Information Technology (IT) Convergence Research Center, and Director of the HOPE-IT Human Resource Development Center, BK21 PLUS, Chonbuk National University. He currently teaches and conducts research in the area of microwave passive and active circuits, mobile and satellite base-station RF systems, design of periodic defected transmission lines, and RF integrated circuit (RFIC) design. He has authored or coauthored over 100 papers in international journals and conference proceedings. Dr. Jeong is a member of the Korea Institute of Electromagnetic Engineering and Science (KIEES).